1. 中断的起源

❝

在1956年,ERA 1103A计算机系统引入了中断(interrupt)机制。

❞

ERA 1103A计算机系统主要用于接收和处理风洞试验数据,并将处理结果返回给风洞进行循环使用。然而,由于风洞数据的准备时间较长,ERA 1103A在等待期间处于空闲状态,这段时间被白白浪费了。为了提高ERA 1103A的利用率,设计者引入了一条中断线,使得在等待风洞数据时可以运行其他程序。当风洞数据准备就绪时,通过中断线通知ERA 1103A停止当前工作并接收风洞数据。

这就是最初中断设计的雏形。

ERA 1103A计算机系统

2. 中断分类

现代处理器的中断概念变得越来越广泛,已经不仅仅局限于外部设备中断。

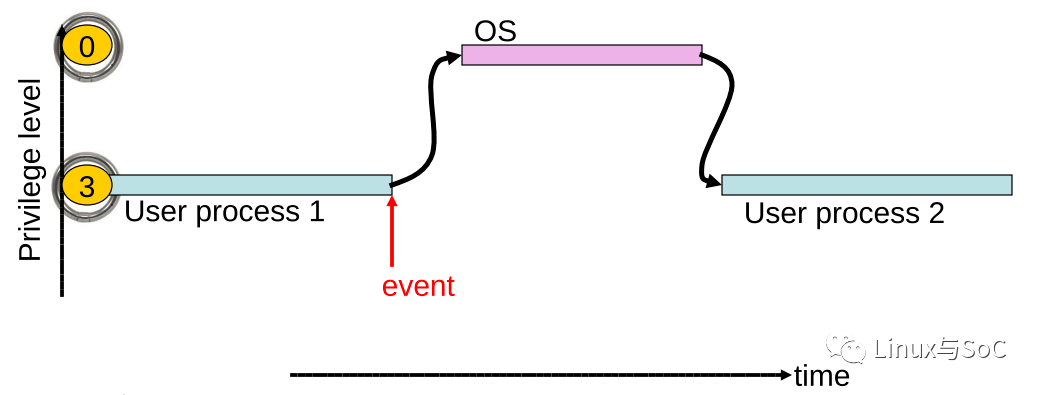

中断存在的意义是CPU控制外部设备的同时,外部设备也可以高效的“控制CPU”。发展至今,这种设计思想扩展到了外部硬件控制CPU、软件控制CPU、CPU运行管理等三个方面。

因此,使用events事件来表示则更加的贴切实际,但在平时描述中,基本上仍然采用了中断这个词。

events的分类如下图所示,主要包括中断和异常,外部硬件控制CPU对应hardware interupt,软件控制CPU对应software interrupt,CPU运行管理则对应exception。

2.1 hardware interrupt

硬件中断是我们平时接触的最多的一类event,比如鼠标、键盘、网卡等等都可以产生硬件中断。因为CPU并不知道外部硬件设备何时产生硬件中断请求,也不会提前获知产生硬件中断的前提,因此,硬件中断属于异步event。

CPU和外部IO设备通过一根或多根硬件连线进行硬件中断信号的传递。这种硬件连线可以在SoC内部实现,也可以在外部PCB板上实现。

当CPU内部集成了中断控制器IP之后,各个IO设备的中断信号线可以在SoC内部连接到中断控制器。例如非常常见的ARM GIC,当然,它不仅可以处理外部IO设备的硬件中断,也可以处理CPU内部之间硬件中断。其内部结构如下图所示:

内部GIC

外部IO设备可以通过中断控制芯片连接到CPU,该类芯片通常称之为PIC。

此类中断控制芯片中最具有代表性的应该是Intel 8259,在微机原理课程中就能找到它的影子。

Intel 8259 PIC

它是为Intel 8085和Intel 8086微处理器设计的可编程中断控制器(PIC)。8259将多个中断输入源组合成一个到主微处理器的单一中断输出,将系统中可用的中断级别扩展到处理器芯片上的一个或两个级别之外。在如今高性能GIC中,仍然可见这种分层次、可扩展的中断架构设计理念。

2.2 software interrupt

假设操作系统阻止非特权代码直接访问系统资源,那么应用程序如何访问这些受保护的资源呢?此时,软件中断就可以实现这一目的。当一个应用软件终止或者它向操作系统请求一些服务时,软件中断就会发生。如果说在软件代码中包含了系统调用,那么可以将software interrupt理解为同步事件。

当CPU接收到一个软件中断信号时,它可能会暂时将控制切换到一个中断处理程序程序,并且内核中被中断挂起的进程(例如,一个程序的运行实例)将在中断被接受后恢复。

应用程序基于系统调用完成应用层和操作系统内核之间的通信,实现对CPU的控制。

2.3 异常

CPU异常发生在各种错误的情况下,例如当访问无效的内存地址或除零时,为了对它们作出反应,产生了异常处理机制。不同架构的处理器对异常类型的定义有所不同,但核心思想是CPU工作过程遇到了不被允许的错误或者强制停止指令等,我们可以将异常做如下分类。

对于Faults异常,通常不影响软件代码的继续运行,此类异常主要包括:

-

除0操作 -

无效操作码 -

设备不可用

对于Traps异常,比较常见的就是JTAG debug。当CPU收到了debug指令后,会进入到异常模式。此类异常主要包括:

-

断点 -

溢出 -

调试指令

对于Abort异常,比较常见的就是取指异常,当我们从RAM中没有正确的获取到待执行指令时,CPU进入到Abort异常。此类异常主要包括:

-

访存错误 -

总线错误 -

cache错误

以上就是良许教程网为各位朋友分享的Linu系统相关内容。想要了解更多Linux相关知识记得关注公众号“良许Linux”,或扫描下方二维码进行关注,更多干货等着你 !

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏

.png)